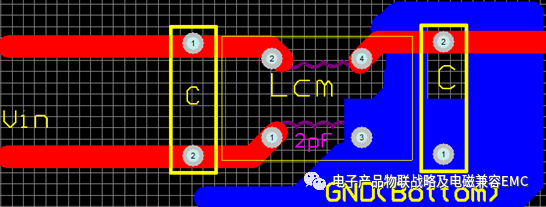

當電子線路中有共模電感的濾波設計時,前后級進行PCB鋪地銅設計時TOP層的走線與BOTTOM底層的PCB鋪地就會存在耦合電容Cp;高頻的騷擾信號就會通過耦合電容影響共模電感的噪聲阻抗性能;等效電路如下:

比如系統的設計LCM器件的雜散電容為2pF;其諧振頻率點在4MHZ左右;進行PCB的鋪地銅的設計由于PCB的布線,其輸入的走線與PCB的鋪地銅帶來有6pF的耦合電容參數;分析如下:

在其LCM的諧振點后就會降低其阻抗值-如上圖的頻率&阻抗特性曲線參考數據;在進行EMI測試時就會帶來高頻>4MHZ的高頻EMI的問題!

在進行PCB雙面板布線鋪銅地的設計時;在某些電路設計中改進PCB布局及走線就可以降低高頻的EMI電磁干擾;簡單優化的PCB設計參考如下:

注意:如果接地層存在噪聲耦合源,則接地層不應靠近敏感輸入電路。

對于雙面板的系統有時鐘信號是很普遍的;系統晶振時鐘頻率高,干擾諧波能量就強;干擾諧波除了從其輸入與輸出兩條布局布線傳導出來還會從空間輻射出來,若布局布線不合理,很容易產生很強的尖峰噪聲輻射問題,因此在PCB 板布局布線時對晶振和CLK 信號線布局非常重要,高頻時鐘信號需要能鏡像回流完整的鋪地銅的設計是很關鍵的。

時鐘源的布局布線簡單說明如下:

A.對于有源晶振:耦合電容應盡量靠近晶振的電源引腳,位置擺放順序:

按電源流入方向,依容值從大到小依次擺放,容值最小的電容最靠近引腳。

B.晶振的外殼必須接地,可將晶振信號源包地設計;防止向外輻射,也可以屏蔽外來信號對晶振的干擾。

C.晶振下面不要布其它走線,保證完全鋪地,同時在晶振的300mil范圍內不要布其它走線,防止晶振噪聲源耦合到其它布線、器件等影響性能。

D.時鐘信號的走線應盡量短,晶振不要放置在PCB板的邊緣!

如果電路板邊緣有復位及數據&地址信號線等等,PCB的板的邊緣都需要進行鋪地銅的設計;保證關鍵信號線的地回流路徑的鏡像對稱性設計。

因此,對于PCB雙面板的鋪銅地不是每個地方按面積來鋪設的,鋪地要有目標的去鋪設才能有好的作用,不正確的鋪地設計反而會惡化系統的EMC性能。

更多設計應用實踐及技術交流;請關注阿杜老師!

杜佐兵

電磁兼容(EMC)線上&線下高級講師

杜佐兵老師在電子行業從業近20年,是國家電工委員會高級注冊EMC工程師,武漢大學光電工程學院、光電子半導體激光技術專家。目前專注于電子產品的電磁兼容設計、開關電源及LED背光驅動設計。

2019年在電源網研討會和大家一起進行交流!

下一站 東莞,成都,上海,杭州……我將理論與實踐分享給大家;

與君探討,我們不見不散!

如果對我以下的課程(課題)感興趣,歡迎邀約和大家分享!

任何的EMC及電子電路的可靠性設計疑難雜癥;先分析再設計才是高性價比的設計!

實際應用中電子產品的EMC涉及面比較廣;我的系統理論及課程再對電子設計師遇到的實際問題進行實戰分析!先分析再設計;實現性價比最優化原則!