FinFET技術已經成為工藝尺寸繼續減小的主要動力。“在可預見的未來,極低的工作電壓與漏電流使得FinFET工藝成為CMOS工藝的標準架構,” ANSYS應用工程高級總監Arvind Shanmugavel說道,“但上述優點是有代價的—電源噪聲問題變得突出。一方面,10納米或7納米的FinFET器件在供電電壓(Vsupply)為500mV時也能可靠地工作;另一方面,門限電壓(Vt)并沒有跟隨工藝節點前進而成比例下降。這樣一來,電壓容限(Vsupply - Vt)急劇減少,設計工程師需要特別注意電源噪聲變化。”

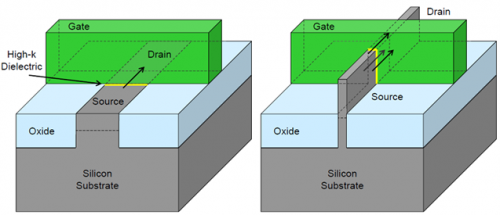

平面工藝與FinFET(右)比較

FinFET工藝獨有的特性帶來了更多的麻煩。“FinFET器件溫度更高,因此白噪聲會增加,” Cadence電源簽核(signoff)產品市場總監Jerry Zhao說,“FinFET器件的三維鰭型結構易聚集熱量,這些熱量會沿垂直方向傳導到鰭型結構上面的走線層。溫度升高增加了噪聲。”

Naviasky補充道:“FinFET架構沒有足夠的去耦電容,所以不能將噪聲去除干凈。有些工藝雖然提供memcap電容,但目前還存在一系列其他的問題。FinFET并沒有帶來新型噪聲,只不過這種技術使噪聲問題更加惡化,并由于去耦電容減少而折磨開發人員。”

在1x納米節點上,不同問題開始相互影響。 “自熱效應很糟糕,但遇上電遷移效應,二者疊加產生的影響更壞(一加一大于二)。” Naviasky繼續解釋,“我們的規則是防止自熱增加的溫度超過5度,否則等不到處理噪聲問題,電遷移問題就會讓你招架不及。”