以前有篇文章講述了時鐘切換的時候毛刺(glitch)帶來的危害,以及如何設計防止毛刺發生的時鐘切換電路。但是沒有講到電路設計的構思從何而來,大家看了之后知道直接用這個電路,但是假如不看這篇文章,自己從頭設計還是無從下手。

在這里,換另外一個角度,通過電路設計技巧來闡述防毛刺時鐘切換電路的設計思路。

希望看過之后,不用參考文章就能夠自己設計出這個電路。

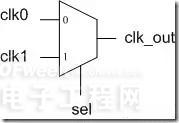

對于一個時鐘切換電路,輸入兩個異步時鐘 clk0、clk1,以及一個選擇信號 sel。

(1) 假設不考慮 glitch,直接使用Mux 就可以完成切頻。電路如下:

由于 clk0/clk1/sel 之間是異步關系,時鐘切換會發生在任意時刻,有一定的概率會發生glitch. glitch 的危害文章里已經詳述,這里不再重復。

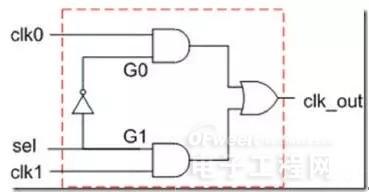

(2) 由于 sel 和 clk0 和 clk1 都是不同步的,我們可以從 sel 同步的方向入手,假如 sel 需要和 clk0和 clk1 進行同步,那么 sel 必須分成兩路,一個和 clk0 同步,一個和 clk1 同步,同步之后的 sel 訊號再和 clk0/clk1 gating 起來,就可以讓問題簡單化。為了將 sel 分成兩路,并且 clk0/clk1 需要分別 gating, 那么可以將 mux 邏輯用and/or設計出來,如下:

當然此 Mux 電路還可以用兩個 or 加上一個 and來實現,都可以。注意 G0 和 G1 兩點就是分別對 clk0 和 clk1進行 gating. 將來會在 G0/G1 點插入同步 DFF.

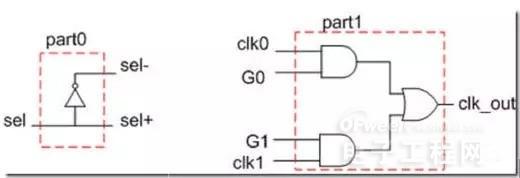

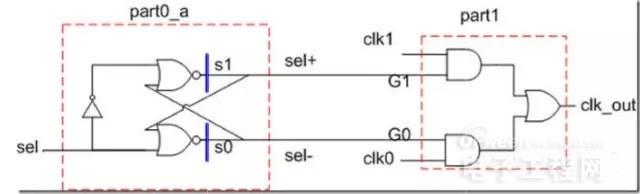

(3) 將上面電路拆開成兩部分,一部分電路通過 sel 產生 sel+和sel-兩路,另一部分電路是 gating mux 電路, 如下:

只需要將 sel-接上 G0, sel+接上 G1 就是一個 mux電路。將電路分開,是為了后續技巧性的功能替換。

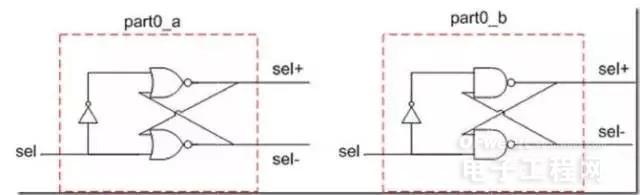

(4) 將 part0 電路換成同樣功能的帶反饋的組合電路(為何要這樣做,屬于電路設計直覺和技巧)。最常見帶反饋的電路是 RS 觸發器,因此可以將 part0 換成如下電路。

(5) 將 part0_a 或者part0_b 替換 part0 電路,功能不變。如下:

不過,此時插入同步DFF 的地方就多了一個選擇,如果直接在G0, G1 插入同步 DFF, clk0 和 clk1 的 gating時間先后順序不確定,還是有可能發生毛刺。而在 s0 和 s1 處插入同步

DFF, 正好利用反饋,讓時鐘切換按照安全的順序進行:

(a)。 先 gating 住之前選擇的時鐘

(b)。 然后再放開將要選擇的時鐘

在(a)和(b)之間,輸出時鐘一直都是無效狀態(對于2and + 1or 的 mux 來說,無效狀態就是 0)

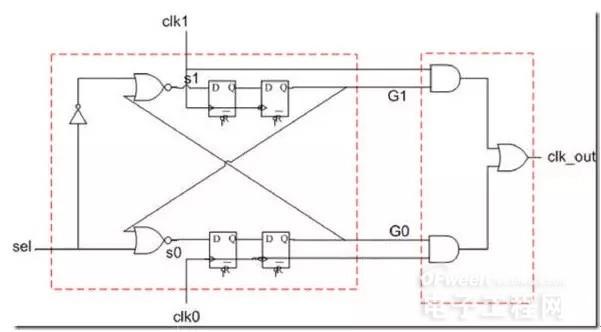

(6) 按照上面的分析,得到電路如下:

注意幾點:

(1) 對 s0插入的 DFF 需要用 clk0 作為時鐘, 對于 s1插入的 DFF 需要用 clk1 作為時鐘。

(2)后一級的 DFF 必須使用 clock 下降沿,因為是用 AND 門進行 gating(如果用上升沿,則更容易出現毛刺)。如果換成 2 個 OR+1個 AND 的 MUX, 則必須用上升沿。

(3)必須插入兩級 DFF 防止 metal stable, 前一級可以用上升沿,也可以用下降沿,用上升沿是為了節省時間。

(4)所有的 DFF 復位值都是 0,即讓 clk_out 處于無效狀態。

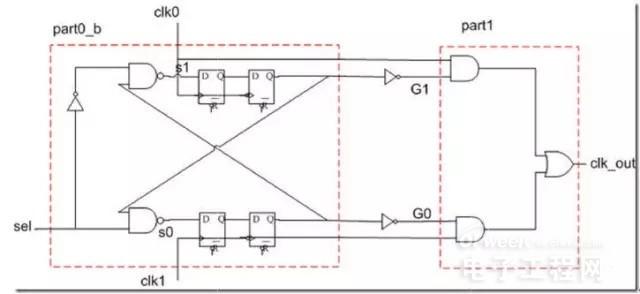

(5)必須滿足先 gating 后放開的順序,如果不滿足,可以在G0/G1 處各插入一個反相器。(用 part0_b搭配 part1 的時候需要插入反相器,如下圖)

(6)搭配不同的 part0電路和part1 電路,經過稍許修改,都可以完成防毛刺切頻電路的設計。