三、 電磁兼容的合理PCB設計

隨著系統設計復雜性和集成度的大規模提高,電子系統設計師們正在從事100MHZ以上的電路設計,總線的工作頻率也已經達到或者超過50MHZ,有的甚至超過100MHZ。當系統工作在50MHz時,將產生傳輸線效應和信號的完整性問題;而當系統時鐘達到120MHz時,除非使用高速電路設計知識,否則基于傳統方法設計的PCB將無法工作。因此,高速電路設計技術已經成為電子系統設計師必須采取的設計手段。只有通過使用高速電路設計師的設計技術,才能實現設計過程的可控性。

通常認為如果數字邏輯電路的頻率達到或者超過45MHZ~50MHZ,而且工作在這個頻率之上的電路已經占到了整個電子系統一定的份量(比如說1/3),就稱為高速電路。實際上,信號邊沿的諧波頻率比信號本身的頻率高,是信號快速變化的上升沿與下降沿(或稱信號的跳變)引發了信號傳輸的非預期結果。要實現符合EMC標準的高頻PCB設計,通常需要采用以下技術:包括旁路與去耦、接地控制、傳輸線控制、走線終端匹配等。

(1)旁路與去耦

去耦是指去除在器件切換時從高頻器件進入到配電網絡中的RF能量,而旁路則是從元件或電纜中轉移不想要的共模RF能量。

所有的電容器都是由LCR電路組成,其中L是電感,它與導線長度有關,R是導線中的電阻,C是指電容。在某一頻率上,該LC串聯組合將產生諧振。在諧振狀態下,LCR電路將有非常小的阻抗和有效的RF旁路。當頻率高于電容的自諧振時,電容器漸變為感性阻抗,同時旁路或去藕效果下降。因此,電容器實現旁路與去耦的效果受引線長度,以及電容器與器件間的走線、介質填料等的影響。理想的去耦電容器還可以提供邏輯裝置狀態切換時所需的所有電流,實際上是電源和接地層間的阻抗決定電容器能夠提供的電流的多少。

當選擇旁路和去耦電容時,可通過邏輯系列和所使用的時鐘速度來計算所需電容器的自諧振頻率,根據頻率以及電路中的容抗來選擇電容值。在選擇封裝尺度是盡量選擇更低引線電感的電容,這通常表現為SMT(Surface Mount Technology)電容器,而不選擇通孔式電容器(如DIP封裝的電容器)。另外在產品設計中,也常常采用并聯去耦電容來提供更大的工作頻帶,減少接地不平衡。在并聯電容系統中,當高于自諧振頻率時,大電容表現感性阻抗并隨頻率增大而增加;而小電容則表現為容性阻抗并隨頻率增加而減少,而且此時整個電容電路的阻抗比單獨一個電容時的阻抗要小。

(2)接地系統

大多數電子產品都要求接地。接地是使噪聲干擾最小化并對電路進行劃分的一個重要方法。接地主要表現在為模擬與數字電路之間提供參考連接以及在PCB的地層和金屬外殼之間提供高頻連接。

PCB經常包含著危險電壓。它包括在電源組件、通信電路、延遲驅動儀表控制、功率交換模塊以及類似的器件中。要使產品符合安全規則,并符合電磁兼容性,必須去掉這些危險電壓,通常的策略就是采用地線或地平面系統。地線(或地平面)實質是信號回流源的低阻抗路徑。由于地線的這種作用,使得地線中可能會有很大的電流存在。因為地線的阻抗不會是零,因而這種電流會產生電位差。當地線中有電位差存在時,對系統的影響就很明顯了:地電位差能夠造成電路的誤動作,使系統工作不正常。

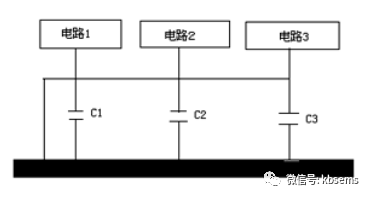

由于接地系統存在地電位差的問題,在設計產品的接地過程中必須針對PCB的特點選擇相應的接地方法,而不能隨意使用。通常采用的接地方法包括單點接地、多點接地、混合接地等。單點接地是指在產品設計中,接地線路與單獨一個參考點相連,這種接地設置目的是為了防止來自兩個不同的參考電平的子系統中的電流與射頻電流經過同樣的返回路徑而導致共阻抗耦合。這種接地方法用在低頻PCB中比較合適,可以減小分布傳輸阻抗的影響。但在高頻PCB中,返回路徑的電感在高頻下成為線路阻抗的主要部分,因而在高頻PCB中為使接地阻抗最小,通常采用多點接地法。多點接地中最重要的一點就是要求接地引線的長度最小,因為更長的引線代表更大的電感,從而增加地阻抗,引起地電位差。混合接地結構是單點接地和多點接地的復合。當在PCB中存在高低混合頻率時常用這種結構,即在低頻處呈現單點接地,而在高頻處則呈現多點接地。如下圖1為容性耦合混合接地。相對應的感性耦合混合接地模型中把C1~C3改為適合的電感即可。